삼성, 업계 최초 3차원 12단 기술 개발…“반도체 패키징 초격차”

업계 최대 용량 24GB HBM 양산 예정

삼성전자는 업계 최초로 D램 12개를 쌓아 수직으로 연결하는 반도체 패키징 기술을 개발하며 반도체 패키징 기술에서 초격차 전략을 펼치고 있다. 삼성전자는 업계 최초로 ‘12단 3D-TSV’(3차원 실리콘 관통전극) 기술 개발에 성공했다고 7일 밝혔다.

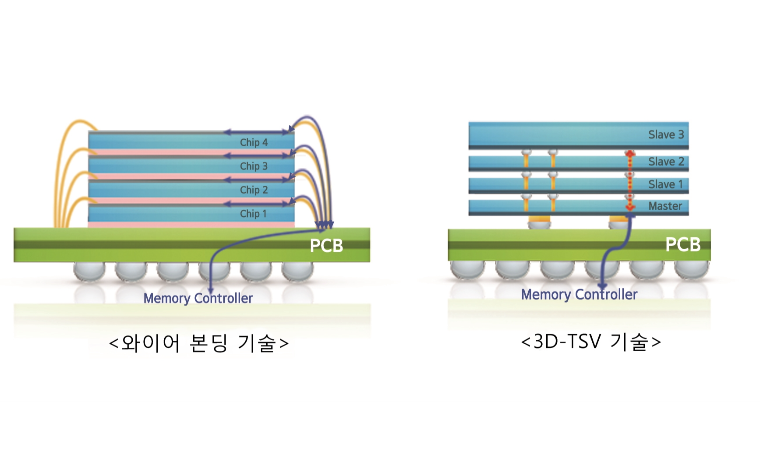

이 기술은 와이어를 이용해 칩을 연결하는 기존 방식(와이어 본딩)과는 달리 반도체 칩 상단과 하단에 머리카락 굵기의 20분의 1 수준에 불과한 미세한 전자 이동통로 6만개를 만들어 연결하는 방식이다. 종이(100㎛)의 절반 이하 두께로 가공한 D램 칩 12개를 쌓아 수직으로 연결하는 고도의 정밀성이 필요하기 때문에 반도체 패키징 기술 가운데 가장 어려운 것으로 평가된다. 특히 ‘와이어 본딩’ 방식보다 칩 사이에 신호를 주고받는 시간이 짧아져 속도와 소비전력을 획기적으로 개선하는 장점이 있다.

이번 기술 개발에 따라 기존 8단 적층 제품(HBM2)과 같은 패키지 두께(720㎛)를 유지하면서도 12개의 D램 칩을 적층할 수 있게 돼 고객사들은 별도의 시스템 디자인 변경 없이도 고성능의 차세대 고용량 제품을 출시할 수 있을 것이라고 회사측은 덧붙였다. 또 고대역폭 메모리에 이 기술을 적용할 경우 기존 8단에서 12단으로 높임으로써 용량도 1.5배 늘릴 수 있다. 이 기술에 최신 16기가비트(Gb) D램 칩을 적용하면 업계 최대 용량인 24기가바이트(GB)급 고대역폭 메모리(HBM) 제품도 구현할 수 있다. 이는 현재 주력 제품으로 양산 중인 8단 8GB 제품보다 용량이 3배 수준이다.

삼성전자는 고객 수요에 따라 ‘12단 3D-TSV’기술을 적용한 업계 최대 용량의 24GB급 고용량 HBM 제품의 양산에 돌입할 예정이라고 밝혔다./김혜영기자jjss1234567@sedaily.com

[ⓒ 서울경제TV(www.sentv.co.kr), 무단 전재 및 재배포 금지]

관련뉴스

- 롯데마트 토이저러스, 마블 테마 KBL 팝업스토어 오픈

- 신세계디에프, 노동부 주관 ‘일·생활 균형 우수기업’ 선정

- 양마니찌개마을, 우수 점포에 기념품 전달

- 유클리드소프트, 통합 보안 플랫폼 ‘SecuAI’ 고도화 속도

- [인사] SPC그룹

- 문구도매쇼핑몰 퍼줌, 유치원·학원 크리스마스선물 신상품 출시

- 글로벌 보안 기업 이반티, 통합 엔드포인트 관리 기능 강화

- 롯데칠성음료, 재생 플라스틱 '칠성사이다 500ml 페트병' 도입

- 한미약품 면역조절 항암 신약 HM16390, 글로벌 단독·병용 임상 순항

- 푸드테크 기업 넷, 고체형 토닉워터 ‘포켓토닉’으로 해외 진출

주요뉴스

기획/취재

주간 TOP뉴스

- 1신애원, ‘2025 꿈키우미서포터즈 초청행사’ 개최

- 2롯데마트 토이저러스, 마블 테마 KBL 팝업스토어 오픈

- 3신세계디에프, 노동부 주관 ‘일·생활 균형 우수기업’ 선정

- 4양마니찌개마을, 우수 점포에 기념품 전달

- 5유클리드소프트, 통합 보안 플랫폼 ‘SecuAI’ 고도화 속도

- 6SPC그룹

- 7문구도매쇼핑몰 퍼줌, 유치원·학원 크리스마스선물 신상품 출시

- 8남원시의회, 5분 자유발언서 도시 시정 전방위 개선 촉구

- 9글로벌 보안 기업 이반티, 통합 엔드포인트 관리 기능 강화

- 102025 용담검무, 남원서 이틀간 전통·무예·예술의 장 열린다

댓글

(0)